近年来,摩尔定律的发展方向似乎遇到了一些瓶颈。按照此前的预期,集成电路的晶体管数量有望每隔一段时间翻番。但现实是,随着制程的不断演进,热管理已成为了芯片突破的一个重要挑战。好消息是,弗吉尼亚大学工程学院和西北大学的研究人员们,刚刚打造了一种基于新型聚合物的电路绝缘材料,特点是能够在较小的空间内达成更高的功率。

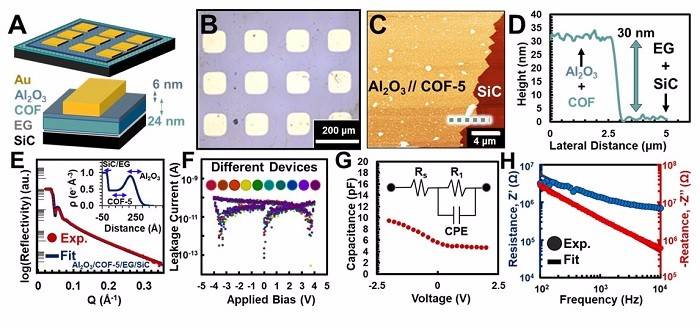

COF-5 介电层阻抗测量(图自:Nature Materials)

据悉,由弗吉尼亚大学机械与航空工程学系教授 Patrick E. Hopkins 和西北大学化学系教授 Will Dichtel 带领的这支多学科研究小组,正在发明一种有望随着尺寸的不断缩小而保持芯片不发高烧的新型材料。

在今日发表于《自然材料》期刊的一篇文章中,他们隆重介绍了一种将电串扰做到最小化的电绝缘材料,且其具有超低的介电常数(ultra-low-k)。

该材料能够通过控制电流以消除信号串扰,使得电子产品能够进一步突破当前的性能极限。理想情况下,它还能够将电流引起的有害热量从电路中带走。

随着芯片制程不断变小和晶体管密度的不断提升,发热造成的困扰也在成倍增长。为此,Patrick E. Hopkins 教授决定寻找一种超低介电常数的新材料。

尽管此前已经相关领域探索了很长一段时间,但除非通过机械工程、化学、材料科学、电气工程等多学科的集思广益,这个目标还是很难单独达成的。

SCITechDaily 指出,Patrick E. Hopkins 教授是该校多功能材料集成计划的领导者之一,并且汇聚了来自多个工程学科的研究人员,以配制出这种具有优异特性的新材料。

研究一作 Ashutosh Giri 表示,化学团队意识到了材料的热特性,接着从更多的维度去探索,而机械与材料团队可以从分子工程水平上去作深入了解。

Will Dichtel 教授补充道,他们正在打造只有一个原子那么厚(简称 2D)的聚合物薄板,并通过在特定的体系结构中对其进行分层,以控制它们的性能。

通过改进生产高质量 2D 聚合物薄膜的方法,研究团队正在积极应用这种新型材料,以满足在致密芯片上让晶体管规模更加密集的小型化要求。

展望未来,这项技术有望在半导体(芯片制造)行业发挥巨大的潜力,因其不仅具有超低介电常数、又具有超高的传热性能。

感兴趣的朋友,可移步至《Nature Materials》查看全文,原标题为《Thermally conductive ultra-low-k dielectric layers based on two-dimensional covalent organic frameworks》。